I den här artikeln kommer vi att gå igenom multiplexern, vi kommer först att definiera vad som är en multiplexer, sedan går vi igenom dess typer som är 2×1 och 4×1, sedan kommer vi att gå igenom implementeringen av 2×1 mux och högre mux med lägre ordning mux, Äntligen kommer vi att avsluta vår artikel med några applikationer, fördelar och några vanliga frågor.

Innehållsförteckning

- Vad är multiplexorer?

- Typer av Mux

- 2×1 multiplexer

- 4×1 multiplexer

- Implementering av olika portar med 2:1 Mux

- Implementering av Higher Order MUX med Lower Order MUX

- Fördelar och nackdelar med MUX

Vad är multiplexorer?

En multiplexer är en kombinationskrets som har många dataingångar och en enda utgång, beroende på kontroll- eller valda ingångar. För N ingångsrader krävs log2(N) urvalsrader, eller motsvarande, för

Multiplexer

Typer av Mux

Mux kan vara av olika typer baserat på input men i den här artikeln kommer vi att gå igenom två huvudtyper av mux som är

- 2×1 Mux

- 4×1 Mux

2×1 multiplexer

2×1 är en grundläggande krets som också är känd 2-till-1 multiplexer som används för att välja en signal från två ingångar och överför den till utgången. 2×1 mux har två ingångslinjer, en utgångslinje och en enda urvalslinje. Den har olika applikationer i digitala system som i mikroprocessor den används för att välja mellan två olika datakällor eller mellan två olika instruktioner.

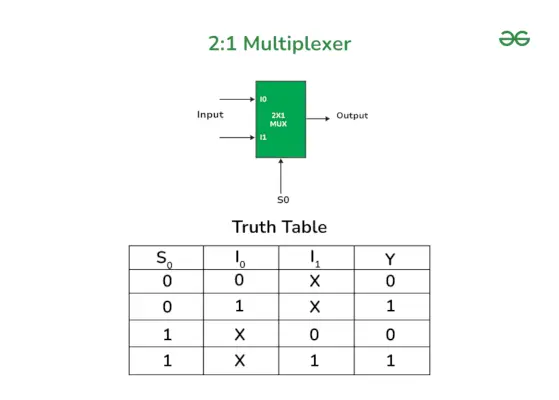

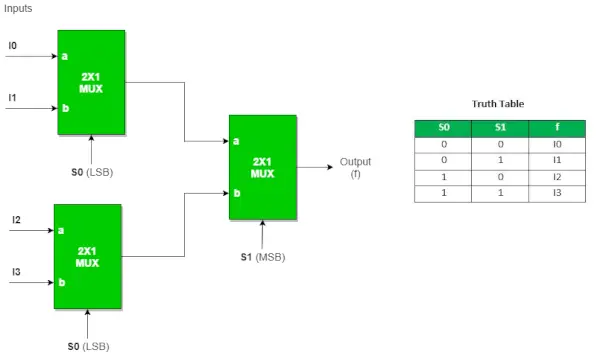

Blockdiagram av 2:1 multiplexer med sanningstabell

Nedan ges blockdiagrammet och sanningstabellen för 2:1 Mux. I detta blockdiagram där I0 och I1 är ingångslinjerna, Y är utgångslinjen och SO är en enda vallinje.

Blockdiagram av 2:1 multiplexer med sanningstabell

Utsignalen från 2×1 Mux kommer att bero på urvalsraden S0,

- När S är 0 (låg) väljs I0

- när S0 är 1(Hög) väljs I1

Logiskt uttryck för 2×1 Mux

Med hjälp av sanningstabellen kan det logiska uttrycket för Mux bestämmas som

Y=overline{S_0}.I_0+S_0.I_1

Kretsdiagram för 2×1 multiplexorer

Med hjälp av sanningstabellen krets diagram kan ges som

Kretsdiagram av 2×1 Mux

4×1 multiplexer

4×1-multiplexern som också är känd som 4-till-1-multiplexern. Det är en multiplexer som har 4 ingångar och en enda utgång. Utgången väljs som en av de 4 ingångarna som baseras på valingångarna. Antalet urvalslinjer kommer att bero på numret på ingången som bestäms av ekvationen

Blockdiagram av 4×1 multiplexer

I det givna blockdiagrammet är I0, I1, I2 och I3 de 4 ingångarna och Y är den enda utgången som är baserad på Välj-linjerna S0 och S1.

Utsignalen från multiplexorn bestäms av det binära värdet för urvalslinjerna

- När S1S0=00 väljs ingången I0.

- När S1S0=01 väljs ingången I1.

- När S1S0=10 väljs ingången I2.

- När S1S0=11 väljs ingången I3.

Sanningstabell för 4×1 multiplexer

Nedan ges Sanningstabell av 4×1 multiplexer

kompatibilitetstestning

Kretsdiagram för 4×1 multiplexorer

Med hjälp av sanningstabellen kan kretsschemat ges som

Multiplexern kan fungera som en universell kombinationskrets. Alla standard logiska grindar kan implementeras med multiplexorer.

Implementering av olika portar med 2:1 Mux

Nedan ges implementeringen av olika grindar med 2:1 Mux

Implementering av NOT-grind med 2 : 1 Mux

Not-porten från 2:1 Mux kan erhållas av

- Anslut insignalen till en av dataingångsledningarna (I0).

- Anslut sedan en linje (0 eller 1) till den andra dataingångslinjen (I1)

- Anslut samma ingångsledning Välj linje S0 som är ansluten till D0.

Nedan ges diagrammet för den logiska representationen av INTE grind med användning av 2:1 Mux

css opacitetsövergång

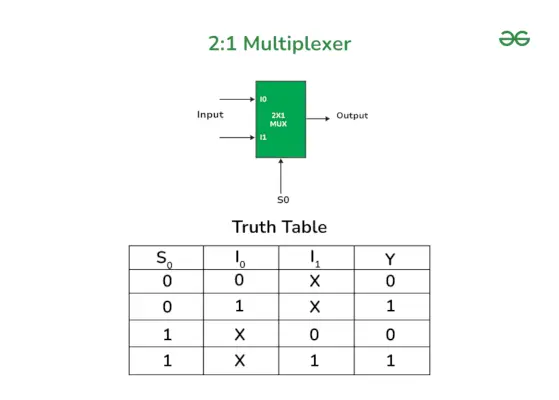

Implementering av AND-grind med 2 : 1 Mux

And-porten från 2:1 Mux kan erhållas av

- Anslut ingång Y till I1.

- Anslut ingång X till urvalslinjen S0.

- Anslut en linje(0) till I0.

Nedan ges diagrammet för den logiska representationen av OCH grind med användning av 2:1 Mux

För ytterligare mer om Implementering av AND-grind med 2 : 1 Mux

Implementering av OR-grind med användning av 2 : 1 Mux

ELLER-grinden från 2:1 Mux kan erhållas genom

- Anslut ingång X till vallinjen S0.

- Anslut ingång Y till I1.

- Anslut linje(1) till I1.

Nedan ges diagrammet för den logiska representationen av ELLER grind med användning av 2:1 Mux

Implementering av NAND, NOR, XOR och XNOR grindar kräver två 2:1 Mux. Första multiplexorn kommer att fungera som NOT-grind som kommer att tillhandahålla kompletterad input till den andra multiplexorn.

Implementering av NAND-grind med användning av 2 : 1 Mux

NAND-grinden från 2:1 Mux kan erhållas genom

- I första mux ta ingångar och 1 och 0 och y som urvalsrad.

- I Second MUX är utgången från mux ansluten till I1.

- line(1) ges till I0.

- x ges som urvalsrad för den andra Mux.

Nedan ges diagrammet för den logiska representationen av NAND-grind med användning av 2:1 Mux

För ytterligare mer om Implementering av NAND-grind med användning av 2 : 1 Mux

Implementering av NOR-grind med 2 : 1 Mux

Nor-porten från 2:1 Mux kan erhållas av

- I första mux ta ingångar och 1 och 0 och y som urvalsrad.

- I Second MUX kopplas utgången från mux till I0.

- linje(0) ges till I1.

- x ges som urvalsrad för den andra Mux.

Nedan ges diagrammet för den logiska representationen av NOR-port med användning av 2:1 Mux

För ytterligare mer om Implementering av NOR-grind med 2 : 1 Mux

Implementering av EX-OR-grind med 2 : 1 Mux

Nor-porten från 2:1 Mux kan erhållas av

- I första mux ta ingångar och 1 och 0 och y som urvalsrad.

- I Second MUX är utgången från mux kopplad till I1.

- y ges till I0.

- x ges som urvalsrad för den andra Mux.

Nedan ges diagrammet för den logiska representationen av EX-OR-grind med användning av 2:1 Mux

Implementering av EX-NOR-grind med 2 : 1 Mux

Nedan ges diagrammet för den logiska representationen av EX-OR-grind med användning av 2:1 Mux

Nor-porten från 2:1 Mux kan erhållas av

- I första mux ta ingångar och 1 och 0 och y som urvalsrad.

- I Second MUX kopplas utgången från mux till I0.

- y ges till I1.

- x ges som urvalsrad för den andra Mux.

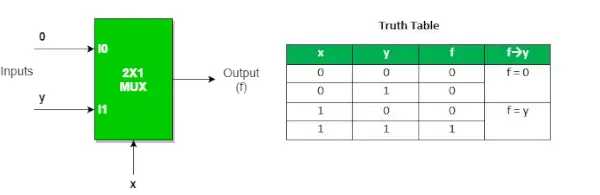

Implementering av Higher Order MUX med Lower Order MUX

Nedan ges implementeringen av Higher Order MUX med lägre Order MUX

4 : 1 MUX med 2 : 1 MUX

Tre 2:1 MUX krävs för att implementera 4:1 MUX.

Liknande,

Medan en 8:1 MUX kräver sju (7) 2:1 MUX, kräver en 16:1 MUX femton (15) 2:1 MUX och en 64:1 MUX kräver sextiotre (63) 2:1 MUX. Därför kan vi dra slutsatsen att en

16 : 1 MUX med 4 : 1 MUX

Nedan ges det logiska diagrammet för 16:1 Mux med 4:1 Mux

I allmänhet, för att implementera B : 1 MUX med A : 1 MUX , används en formel för att implementera densamma.

B/A = K1,

K1/A = K2,

K2/A = K3

KN-1/ A = KN= 1 (tills vi får 1 antal MUX).

Lägg sedan till alla MUX-tal = K1 + K2 + K3 + …. + KN.

För att implementera 64 : 1 MUX med 4 : 1 MUX

Med hjälp av ovanstående formel kan vi få detsamma.

64/4 = 16

16/4 = 4

4/4 = 1 (tills vi får 1 antal MUX)

Därför krävs totalt antal 4:1 MUX för att implementera 64:1 MUX = 16 + 4 + 1 = 21.

f (A, B, C) =

med A och B som valrader för 4:1 MUX,

AB som välj: Expandera minterms till dess booleska form och kommer att se dess 0 eller 1 värde på C:e plats så att de kan placeras på det sättet.

AC som välj : Expandera minterms till dess booleska form och kommer att se dess 0 eller 1 värde på Bth plats så att de kan placeras på det sättet.

BC som välj : Expandera minterms till sin booleska form och kommer att se dess 0 eller 1 värde i Athplats så att de kan placeras på det sättet.

Fördelar och nackdelar med MUX

Nedan ges fördelarna och nackdelarna med MUX

Fördelar med MUX

Nedan ges fördelarna med MUX

- Effektivitet : Mux har god effektivitet när det gäller att dirigera flera insignaler till en enda utsignal baserat på styrsignaler.

- Optimering : Mux hjälper till att spara resurser som ledningar, stift och integrerad krets (IC).

- Olika implementeringar: Mux kan användas för att implementera olika digitala logiska funktioner såsom AND,OR etc.

- Flexibilitet: Mux kan enkelt konfigureras enligt kraven och rymma olika datakällor, vilket förbättrar systemets mångsidighet.

Nackdelar med MUX

Nedan ges nackdelarna med MUX

- Begränsat antal datakällor: Antalet indata som kan tas av en multiplexor begränsas av antalet kontrolllinjer, vilket kan orsaka begränsningar i vissa applikationer.

- Dröjsmål: Multiplexorer kan ha en viss fördröjning i signalvägen, vilket kan påverka kretsens prestanda.

- Komplex kontrollmotivering: Styrlogiken för multiplexorer kan vara komplex, särskilt för större multiplexorer med ett stort antal ingångar.

- Strömutnyttjande: Multiplexorer kan förbruka mer ström jämfört med andra enkla l ogisk port , särskilt när de har ett stort antal ingångar.

Tillämpningar av MUX

Nedan ges applikationerna för MUX

- Datarouting : Mux används för datarouting i det digitala systemet där de väljer en av de flera datalinjerna och dirigerar om den till utgången.

- Dataval : Mux används för dataval där de väljer datakälla enligt valraderna.

- Analog-till-digital konvertering : Mux används i ADC för att välja olika analoga ingångskanaler.

- Adressavkodning : Mux används i Mikroprocessorer eller minne för adressavkodning.

- Implementering av logiska funktioner : Muxes kan användas för att implementera olika logiska funktioner.

Slutsats

I den här artikeln har vi gått igenom MUX, vi har sett olika typer av Mux som är 2×1 och 4×1 Mux, vi har gått igenom implementeringen av 2×1 mux och högre mux med lägre ordningsmux. Vi har också gått igenom dess fördelar, nackdelar och tillämpningar i korthet.

java undantag

Multiplexorer i digital logik – vanliga frågor

Varför anses styrlogiken för multiplexorer vara komplex?

Mux kan vara komplex speciellt för större multiplexorer på grund av styrsignalerna som väljer ingångar baserat på applikationskraven.

Vilka är de olika typerna av multiplexerarkitekturer?

Mux-arkitekturer ändras på faktorer som det totala antalet ingångar, antalet urvalslinjer och logiken som används för val av ingång.

Hur används multiplexorer för digital signalbehandling (DSP)?

I DSP-applikationer används multiplexorer för signaldirigering, urval och bearbetning.