Flip-flop är en term som hör till digital elektronik, och det är en elektronisk komponent som används för att lagra en enda bit information.

Diagrammatisk representation av flip flop

- Eftersom flip flop är en sekventiell krets baseras dess ingång på två parametrar, den ena är strömingången och den andra är utgången från det tidigare tillståndet.

- Den har två utgångar, båda är komplement till varandra.

- Det kan vara i ett av två stabila tillstånd, antingen 0 eller 1.

Grundläggande diagram av flip flop

Vad är T Flip Flop?

- T flip flop eller för att vara exakt är känd som Toggle Flip Flop eftersom den kan växla sin utgång beroende på ingången.

- T här står för Växla .

- Växla indikerar i princip att biten kommer att vändas, det vill säga antingen från 1 till 0 eller från 0 till 1.

- Här tillförs en klockpuls för att driva denna flopp, så det är en klockad flip-flop.

Konstruktion av T Flip Flop

Vi kan konstruera T flip på tre sätt, nämligen:

- Genom att använda SR Flip Flops.

- Genom att använda D Flip Flops.

- Genom att använda JK Flip Flops

Sätt att konstruera T Flip Flop

Låt oss se konstruktionen av T Flip Flops med SR Flip Flops, som kräver 2 AND-grindar och 2 NOR-grindar som visas nedan:

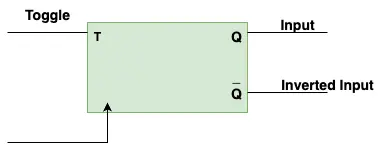

Grundläggande blockdiagram av T Flip Flop

Här innehåller blockschemat Toggle och klockingångar, Q och Q' är de kompletterade ingångarna.

T Flip Flop fungerar

Fall 1 : Låt oss säga, T = 0 och klockpulsen är hög dvs 1, då kommer utsignalen från båda, OCH-grind 1, OCH-grind 2 att vara 0 , grind 3 output kommer att vara F och liknande grind 4 output kommer att vara Q' så båda värdena för Q och Q' är samma som deras tidigare värde, vilket betyder Håll tillstånd .

Fall 2 : Låt oss säga, T=1 , då kommer utgången från både OCH-grind 1 att vara (T * klocka * Q) , och eftersom T och klockan båda är 1, kommer utgången från OCH-grind 1 att vara F och på liknande sätt kommer utsignalen från OCH-grinden 2 att vara (T * klocka * Q') dvs. Q' . Nu kommer gate 3-utgången att vara (Q'+Q)' och låt oss säga att Q' är noll, då kommer gate 3-utgången att vara (0+Q)' som betyder Q' och på liknande sätt kommer grind 4-utgång att vara (Q+Q’)’ och eftersom Q' är noll, så kommer grind 4-utgången att vara Q' vilket betyder 0 eftersom Q' är noll. Därför kan vi i det här fallet säga att utgången växlar, eftersom T=1 .

Truth Table of T Flip Flop

- Här är T växlingsingången, Q är nuvarande tillståndsingång, Qt+1 är nästa tillståndsutgång.

- Härifrån kan vi se att närhelst Toggle (T) är 0, är nästa tillståndsutgång (Qt+1) densamma som nuvarande tillståndsingång (Q).

- Närhelst Toggle (T) är 1, kommer nästa tillståndsutgång (Qt+1) att vara ett komplement till nuvarande tillståndsingång (Q), vilket betyder att den växlas.

Karakteristisk ekvation

- Den karakteristiska ekvationen berättar om vad som kommer att bli nästa tillstånd av flip flop i termer av nuvarande tillstånd.

- För att få den karakteristiska ekvationen konstrueras K-Map som kommer att visas enligt nedan:

- Om vi löser ovanstående K-Map så blir den karakteristiska ekvationen Q(n+1) = TQn’ + T’Qn = T XELLER Qn

Excitationstabell

Excitationstabellen berättar i princip om den excitation som krävs av flip flop för att gå från nuvarande tillstånd till nästa tillstånd.

- Här, närhelst T är 0, är Qt+1 samma som input Q.

- Och närhelst T är 1 är Qt+1 komplement till ingång Q.

Tillämpningar av T Flip Flop

Det finns många tillämpningar av T Flip Flop i Digital System, som listas nedan:

- Räknare : T Flip Flops som används i diskar. Räknare räknar antalet händelser som inträffar i ett digitalt system.

- Datalagring : T Flip Flops används för att skapa minne som används för att lagra data när strömmen är avstängd.

- Synkrona logiska kretsar : T flip-flops kan användas för att implementera synkrona logiska kretsar, som är kretsar som utför operationer på binär data baserat på en klocksignal. Genom att synkronisera logikkretsens operationer till klocksignalen med hjälp av T-vippor, kan kretsens beteende göras förutsägbart och tillförlitligt.

- Frekvensuppdelning : Den används för att dividera frekvensen för en klocksignal med 2. Vippan växlar dess utsignal varje gång klocksignalen övergår från hög till låg eller låg till hög, och dividerar därför klockfrekvensen med 2.

- Skiftregister : T vippor kan användas i skiftregister som används för att skifta binär data i en riktning.

Slutsats

I den här artikeln utgår vi från grunderna för flip flops, att vad som faktiskt är flip flops och sedan diskuterade vi om T flip flops, tre två sätt på vilka vi kan konstruera T flip flops, det är Basic Block Diagram, Working of T Flip Flops , det är sanningstabellen, karakteristiska ekvationen samt excitationstabellen och till slut diskuterade vi tillämpningarna av T flip flops.